kissste

Member

The last piece has has arrived - RDA5981C+RDA5856EQ

1/ Firmware/flash is different

It has got Dueros support and playback/microphone functions

AT+H

+OK:AT - AT mode

+OK:AT+H - check AT help

+OK:AT+ECHO - open/close uart echo

+OK:AT+RST - Software Reset

+OK:AT+GMI - get factory information

+OK:AT+VER - get version

+OK:AT+UART - set/get serial baudrate

+OK:AT+USERDATA - write/read user data

+OK:AT+SLEEP - enable/disable sleep

+OK:AT+WAKESRC - set wakeup source

+OK:AT+RESTORE - restore default config

+OK:AT+WSMAC - set/get mac address

+OK:AT+WSSCAN - scan AP

+OK:AT+WSCONN - start wifi connect

+OK:AT+WSDISCONN - disconnect

+OK:AT+WDBG - adjust debug level

+OK:AT+WSC - start smart config

+OK:AT+WSFIXIP - enable/disable DHCP

+OK:AT+WAP - enable AP

+OK:AT+WAPSTOP - stop AP

+OK:AT+WAMAC - set/get softap mac address

+OK:AT+WSAK - start wechat airkiss

+OK:AT+WASTA - get joined sta info

+OK:AT+WANET - set/get AP net info

+OK:AT+NSTART - start tcp/udp client

+OK:AT+NSTOP - stop tcp/udp client

+OK:AT+NSEND - send tcp/udp data

+OK:AT+NMODE - start transparent transmission mode

+OK:AT+NCFG - net erase/query/set auto connect config param

+OK:AT+NLINK - check tcp/udp client status

+OK:AT+NPING - do ping

+OK:AT+NDNS - do dns

+OK:AT+BOOTADDR - do bootaddr

+OK:AT+SSTART - start server

+OK:AT+SSTOP - stop server

+OK:AT+SSEND - server send data to client

+OK:AT+SMODE - start server transparent transmission mode

+OK:AT+SLINK - check client status

+OK:AT+SCFG - server erase/query/set auto start/serial param

+OK:AT+FCREATE - bytetd create flash size

+OK:AT+FWRITE - bytetd write flash size

+OK:AT+FREAD - bytetd read flash size

+OK:AT+FDEL - bytetd delete flash size

+OK:AT+FSIZE - bytetd set/get flash size

+OK:AT+FLIST - bytetd list flash file

+OK:AT+FFORMAT - bytetd format flash filesys

+OK:AT+FCFG - bytetd query support max flash filenum and max flash file size

+OK:AT+BYTST - bytetd product test

+OK:AT+MSTART - mqtt start

+OK:AT+MSTOP - mqtt stop

+OK:AT+MSUB - mqtt subscribe

+OK:AT+MUSUB - mqtt unsubscribe

+OK:AT+MPUB - mqtt publish

+OK:AT+MMODE - mqtt transmode

+OK:AT+MCFG - mqtt erase/query/set auto connect config param

+OK:AT+DSKEXI - query sd/udisk dsk/file/diectory exist or not

+OK:AT+DSKRD - read sd/udisk file

+OK:AT+DSKWR - write sd/udisk file

+OK:AT+DSKDEL - delete sd/udisk file/directory

+OK:AT+DSKCR - create sd/udisk file/directory

+OK:AT+IORD - gpio read

+OK:AT+IOWR - gpio write

+OK:AT+IODIR - set/get gpio direction

+OK:AT+ADC - adc read

+OK:AT+VBAT - read vbat value

+OK:AT+PWM - pwm out

+OK:AT+BYUPDATE - bytetd module firmware update

+OK:AT+ZZVER - zzcloud version

+OK:AT+ZZREG - zzcloud register

+OK:AT+ZZACT - zzcloud activate device

+OK:AT+ZZID - query zzcloud authid

+OK:AT+ZZQR - query zzcloud qrcode

+OK:AT+ZZSTART - zzcloud start

+OK:AT+ZZSTOP - zzcloud stop

+OK:AT+ZZSEND - zzcloud send

+OK:AT+ZZSENDEX - zzcloud sendex

+OK:AT+ZZFUNC - zzcloud func

+OK:AT+DUVER - dueros version

+OK:AT+DUSTART - dueros start

+OK:AT+DUSTOP - dueros stop

+OK:AT+DUPLAY - dueros play

+OK:AT+DUVOL - dueros set volume

+OK:AT+DUREC - dueros start or stop record

+OK:AT+DUPAUSE - dueros pause or play

+OK:AT+DUNEXT - dueros play next

+OK:AT+DUPRE - dueros play previous

+OK:AT+DUREP - dueros repeat play

+OK:AT+DUNAME - dueros set/get dlna name

+OK:AT+DUCFG - dueros erase/query/set auto connect config param

+OK:AT+AUTST - audio factory test

+OK:AT+AUVER - audio version

+OK:AT+AUMODE - audio start

+OK:AT+AUPLAY - audio play

+OK:AT+AUSTOP - audio stop

+OK:AT+AUPAUSE - audio pause or resume

+OK:AT+AUVOL - audio set volume

+OK:AT+AUREC - audio record to file

+OK:AT+AUNEXT - audio next sd file

+OK:AT+AUPRE - audio previous sd file

+OK:AT+AUREP - audio repeat sd file

+OK:AT+AULIST - audio list all sd files

AT+VER

+OK:V01.03.0320171206B028

AT+GMI

+OK:Shenzhen Bytetd Technology Co.LTD

+OK:R01C

AT+DUVER

+DUVER:V1.2.4(BETA)

AT+AUVER

+AUVER:5856-100-171020-112235-M1H31

1/a/ other version of firmware is available here, that one even does bluetooth functionality enabled

RDA5981&RDA5856软件版本更新 - 第3页 - Wi-Fi - 锐迪科技术社区 - Powered by RDA SpreadLink

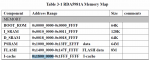

2/ ROM of RDA5981A and C is identical

but dsize in bytes appears to be overflowing. Must have more flash or an additional RAM (PSRAM)

RDA Wlan Boot ROM for RDA5991H v1.0

Build Time: 07:20:54 - Jan 24 2017

RDA Microelectronics Copyright(C) 2004-2017

Enter Mcu Mode

count_left=5

count_left=4

count_left=3

count_left=2

count_left=1

Ready to boot...

Partition addr:4010901c

Find newest partition index:0, total:1, buf_addr:0x00100000, size:0x00000138

Partition[0] info

flag:00000001, version:rda5991h

p_address:00001000, r_address:00001000, psize_in_bytes:0x000cc000, dsize_in_b▒H▒ ▒/▒ `A ba▒▒ą▒Ą▒▒▒▒b

1/ Firmware/flash is different

It has got Dueros support and playback/microphone functions

AT+H

+OK:AT - AT mode

+OK:AT+H - check AT help

+OK:AT+ECHO - open/close uart echo

+OK:AT+RST - Software Reset

+OK:AT+GMI - get factory information

+OK:AT+VER - get version

+OK:AT+UART - set/get serial baudrate

+OK:AT+USERDATA - write/read user data

+OK:AT+SLEEP - enable/disable sleep

+OK:AT+WAKESRC - set wakeup source

+OK:AT+RESTORE - restore default config

+OK:AT+WSMAC - set/get mac address

+OK:AT+WSSCAN - scan AP

+OK:AT+WSCONN - start wifi connect

+OK:AT+WSDISCONN - disconnect

+OK:AT+WDBG - adjust debug level

+OK:AT+WSC - start smart config

+OK:AT+WSFIXIP - enable/disable DHCP

+OK:AT+WAP - enable AP

+OK:AT+WAPSTOP - stop AP

+OK:AT+WAMAC - set/get softap mac address

+OK:AT+WSAK - start wechat airkiss

+OK:AT+WASTA - get joined sta info

+OK:AT+WANET - set/get AP net info

+OK:AT+NSTART - start tcp/udp client

+OK:AT+NSTOP - stop tcp/udp client

+OK:AT+NSEND - send tcp/udp data

+OK:AT+NMODE - start transparent transmission mode

+OK:AT+NCFG - net erase/query/set auto connect config param

+OK:AT+NLINK - check tcp/udp client status

+OK:AT+NPING - do ping

+OK:AT+NDNS - do dns

+OK:AT+BOOTADDR - do bootaddr

+OK:AT+SSTART - start server

+OK:AT+SSTOP - stop server

+OK:AT+SSEND - server send data to client

+OK:AT+SMODE - start server transparent transmission mode

+OK:AT+SLINK - check client status

+OK:AT+SCFG - server erase/query/set auto start/serial param

+OK:AT+FCREATE - bytetd create flash size

+OK:AT+FWRITE - bytetd write flash size

+OK:AT+FREAD - bytetd read flash size

+OK:AT+FDEL - bytetd delete flash size

+OK:AT+FSIZE - bytetd set/get flash size

+OK:AT+FLIST - bytetd list flash file

+OK:AT+FFORMAT - bytetd format flash filesys

+OK:AT+FCFG - bytetd query support max flash filenum and max flash file size

+OK:AT+BYTST - bytetd product test

+OK:AT+MSTART - mqtt start

+OK:AT+MSTOP - mqtt stop

+OK:AT+MSUB - mqtt subscribe

+OK:AT+MUSUB - mqtt unsubscribe

+OK:AT+MPUB - mqtt publish

+OK:AT+MMODE - mqtt transmode

+OK:AT+MCFG - mqtt erase/query/set auto connect config param

+OK:AT+DSKEXI - query sd/udisk dsk/file/diectory exist or not

+OK:AT+DSKRD - read sd/udisk file

+OK:AT+DSKWR - write sd/udisk file

+OK:AT+DSKDEL - delete sd/udisk file/directory

+OK:AT+DSKCR - create sd/udisk file/directory

+OK:AT+IORD - gpio read

+OK:AT+IOWR - gpio write

+OK:AT+IODIR - set/get gpio direction

+OK:AT+ADC - adc read

+OK:AT+VBAT - read vbat value

+OK:AT+PWM - pwm out

+OK:AT+BYUPDATE - bytetd module firmware update

+OK:AT+ZZVER - zzcloud version

+OK:AT+ZZREG - zzcloud register

+OK:AT+ZZACT - zzcloud activate device

+OK:AT+ZZID - query zzcloud authid

+OK:AT+ZZQR - query zzcloud qrcode

+OK:AT+ZZSTART - zzcloud start

+OK:AT+ZZSTOP - zzcloud stop

+OK:AT+ZZSEND - zzcloud send

+OK:AT+ZZSENDEX - zzcloud sendex

+OK:AT+ZZFUNC - zzcloud func

+OK:AT+DUVER - dueros version

+OK:AT+DUSTART - dueros start

+OK:AT+DUSTOP - dueros stop

+OK:AT+DUPLAY - dueros play

+OK:AT+DUVOL - dueros set volume

+OK:AT+DUREC - dueros start or stop record

+OK:AT+DUPAUSE - dueros pause or play

+OK:AT+DUNEXT - dueros play next

+OK:AT+DUPRE - dueros play previous

+OK:AT+DUREP - dueros repeat play

+OK:AT+DUNAME - dueros set/get dlna name

+OK:AT+DUCFG - dueros erase/query/set auto connect config param

+OK:AT+AUTST - audio factory test

+OK:AT+AUVER - audio version

+OK:AT+AUMODE - audio start

+OK:AT+AUPLAY - audio play

+OK:AT+AUSTOP - audio stop

+OK:AT+AUPAUSE - audio pause or resume

+OK:AT+AUVOL - audio set volume

+OK:AT+AUREC - audio record to file

+OK:AT+AUNEXT - audio next sd file

+OK:AT+AUPRE - audio previous sd file

+OK:AT+AUREP - audio repeat sd file

+OK:AT+AULIST - audio list all sd files

AT+VER

+OK:V01.03.0320171206B028

AT+GMI

+OK:Shenzhen Bytetd Technology Co.LTD

+OK:R01C

AT+DUVER

+DUVER:V1.2.4(BETA)

AT+AUVER

+AUVER:5856-100-171020-112235-M1H31

1/a/ other version of firmware is available here, that one even does bluetooth functionality enabled

RDA5981&RDA5856软件版本更新 - 第3页 - Wi-Fi - 锐迪科技术社区 - Powered by RDA SpreadLink

2/ ROM of RDA5981A and C is identical

but dsize in bytes appears to be overflowing. Must have more flash or an additional RAM (PSRAM)

RDA Wlan Boot ROM for RDA5991H v1.0

Build Time: 07:20:54 - Jan 24 2017

RDA Microelectronics Copyright(C) 2004-2017

Enter Mcu Mode

count_left=5

count_left=4

count_left=3

count_left=2

count_left=1

Ready to boot...

Partition addr:4010901c

Find newest partition index:0, total:1, buf_addr:0x00100000, size:0x00000138

Partition[0] info

flag:00000001, version:rda5991h

p_address:00001000, r_address:00001000, psize_in_bytes:0x000cc000, dsize_in_b▒H▒ ▒/▒ `A ba▒▒ą▒Ą▒▒▒▒b

Последнее редактирование: