pvvx

Активный участник сообщества

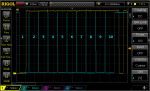

Реальные задачи могут содержать множество вызовов отдельных процедур, которые будут кэшироваться по мере их вызова. И скорость выполнения может ещё больше просесть.

В принципе так оно пашет в любой задаче WiFi с MQTT - там кода более мегабайта и он в жизнь не влезает в кэш и ESP тупит по черному.

В принципе так оно пашет в любой задаче WiFi с MQTT - там кода более мегабайта и он в жизнь не влезает в кэш и ESP тупит по черному.