-

Уважаемые посетители сайта esp8266.ru!

Мы отказались от размещения рекламы на страницах форума для большего комфорта пользователей.

Вы можете оказать посильную поддержку администрации форума. Данные средства пойдут на оплату услуг облачных провайдеров для сайта esp8266.ru -

Система автоматизации с открытым исходным кодом на базе esp8266/esp32 микроконтроллеров и приложения IoT Manager. Наша группа в Telegram

Обсуждение MT7688AN HLK-7688A

- Автор темы aloika

- Дата начала

это чудо инженерной мысли я уже видел) да, работает...нет транса, а по резистору на выход и вход чипа и 2 кондера с каждого резистора на пару в разъеме... Плохо безусловно, но работает.

Вложения

-

485.9 KB Просмотры: 30

pvvx

Активный участник сообщества

Но с условиями! Точно не помню, но требует или прямо комп или роутер.это чудо инженерной мысли я уже видел) да, работает...

Различие в том, что у вас и выходит, т.к. комп или ваш хаб разрывает соединение при настройке куда и чего подключено (перехлест или нет) и определения скорости...

А вот роутер держит стабильно линии и не дергается, не вызывая эксцессов у модуля.

Остальное делайте хоть по этому https://esp8266.ru/forum/threads/mt7688an-hlk-7688a.2934/#post-59964

pvvx

Активный участник сообщества

Ещё это попробуйте (на модуле с прошивкой по умолчанию так):

SDK 5.0.S.0

[ 0.000000] Linux version 3.10.14 (root@ubuntu) (gcc version 4.8.3 (OpenWrt/Linaro GCC 4.8-2014.04 unknown) ) #42 Mon Feb 18 16:05:35 CST 2019

[ 0.000000] console [ttyS1] enabled

...

Press the [f] key and hit [enter] to enter failsafe mode

Press the [1], [2], [3] or [4] key and hit [enter] to select the debug level

...

Может надписи не выводит, а работает...

SDK 5.0.S.0

[ 0.000000] Linux version 3.10.14 (root@ubuntu) (gcc version 4.8.3 (OpenWrt/Linaro GCC 4.8-2014.04 unknown) ) #42 Mon Feb 18 16:05:35 CST 2019

[ 0.000000] console [ttyS1] enabled

...

Press the [f] key and hit [enter] to enter failsafe mode

Press the [1], [2], [3] or [4] key and hit [enter] to select the debug level

...

Может надписи не выводит, а работает...

не работает, уже пробовал((Может надписи не выводит, а работает...

Так... свою проблему решил...

нашел на схемах других плат, что трансформатор для MT7688 средней точкой не подключается ни к чему.

делал по опыту RT5350(HLK-RM04), там средняя точка подключается к VDD1.8v. (без этого не работает)

У других средний провод подтянут к земле.

Здесь же, видимо, по схеме PUSH-PULL выводы сделаны (для знакомых со звуковыми усилителями схема МОСТ).

решил сделать напрямую без деталей совсем.

В RJ45 обжал 2 пары по "B"-варианту, с другой стороны припаял к "гребенке" [MDI_TP_P1/MDI_TN_P1 +MDI_RP_p1/MDI_RN_P1]

Длина 10 см. воткнул в свич - заиграло, прошилось.

@pvvx, спасибо за идеи.

Главное - помогло. Хоть и пришлось самому в схемотехнике покопаться поглубже.

нашел на схемах других плат, что трансформатор для MT7688 средней точкой не подключается ни к чему.

делал по опыту RT5350(HLK-RM04), там средняя точка подключается к VDD1.8v. (без этого не работает)

У других средний провод подтянут к земле.

Здесь же, видимо, по схеме PUSH-PULL выводы сделаны (для знакомых со звуковыми усилителями схема МОСТ).

решил сделать напрямую без деталей совсем.

В RJ45 обжал 2 пары по "B"-варианту, с другой стороны припаял к "гребенке" [MDI_TP_P1/MDI_TN_P1 +MDI_RP_p1/MDI_RN_P1]

Длина 10 см. воткнул в свич - заиграло, прошилось.

@pvvx, спасибо за идеи.

Главное - помогло. Хоть и пришлось самому в схемотехнике покопаться поглубже.

pvvx

Активный участник сообщества

та тама не схемотехника, а кривой boot. Не правильные задержки и кишмиш с опросом контроллера...Главное - помогло. Хоть и пришлось самому в схемотехнике покопаться поглубже.

Именно та китайщина, что и всегда ранее имели в веду...

После загрузки оно и на соплях работает, с нормальными дровами. Да глючит и корючит, но пересогласовывается и вытягивает...

pvvx

Активный участник сообщества

Ну не смогли написать нормально на LAN, но зачем тогда убрали "0" ?

RESET MT7628 PHY!!!!!!

Please choose the operation:

0: Load system code then write to Flash via SERIAL.

1: Load system code to SDRAM via TFTP.

2: Load system code then write to Flash via TFTP.

3: Boot system code via Flash (default).

4: Entr boot command line interface.

5: Load system code then write to Flash via USB Storage.

7: Load Boot Loader code then write to Flash via Serial.

8: Start Web Server to load system code.

9: Load Boot Loader code then write to Flash via TFTP.

И вообще - в каком состоянии надо быть, чтобы в единственный UART одним кодиком на любой Baud остановить загрузку навсегда?

RESET MT7628 PHY!!!!!!

Please choose the operation:

0: Load system code then write to Flash via SERIAL.

1: Load system code to SDRAM via TFTP.

2: Load system code then write to Flash via TFTP.

3: Boot system code via Flash (default).

4: Entr boot command line interface.

5: Load system code then write to Flash via USB Storage.

7: Load Boot Loader code then write to Flash via Serial.

8: Start Web Server to load system code.

9: Load Boot Loader code then write to Flash via TFTP.

И вообще - в каком состоянии надо быть, чтобы в единственный UART одним кодиком на любой Baud остановить загрузку навсегда?

Это то самое, чего не хватало в моем случае))) да, долго, но работало бы без бубнов))Ну не смогли написать нормально на LAN, но зачем тогда убрали "0" ?

RESET MT7628 PHY!!!!!!

Please choose the operation:

0: Load system code then write to Flash via SERIAL.

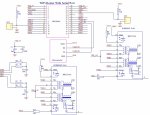

пару картинок для пояснений:

RT5350(HLK-RM04) vs MT7688AN(HLK-7688A)

Вложения

-

174.6 KB Просмотры: 45

Файлы не все прикрепились.

Вложения

-

174.6 KB Просмотры: 23

-

96.8 KB Просмотры: 33

lublupospat

New member

Приветствую всех

HLK-7688A

собрана прошивка 19.07.1

Стоит

kmod-i2c-code

kmod-i2c-mt7628

i2c-tools

kmod-hwmon-core

kmod-hwmon-ads1015

Может кто сталкивался

Вопрос по hwmon. Точнее kmod-hwmon-ads1015 модулю

в /sys/class/hwmon пусто

HLK-7688A

собрана прошивка 19.07.1

Стоит

kmod-i2c-code

kmod-i2c-mt7628

i2c-tools

kmod-hwmon-core

kmod-hwmon-ads1015

Может кто сталкивался

Вопрос по hwmon. Точнее kmod-hwmon-ads1015 модулю

в /sys/class/hwmon пусто

Прошу прощения, может это уже и "некро-ответ", но всё-же.

Насколько мне известно побитовое ИЛИ устанавливает в 1 результат бита, где хотя-бы один из двух (а или b) имеет этот бит равным 1 ?

Далее, выражение ( 1<<12 ) подразумевает сдвиг 1 на 12 бит влево, т.е. все остальные биты это нули, результат-же такой 0x00001000 или в двоичном виде b 000 0000 0000 0000 0000 1000 0000 00000.

Побитовое ИЛИ для 0xFFFFFFFF | 0x00001000 = > 0xFFFFFFFF (что вполне естественно). Если поставить просто знак равенства, то регистр будет заполнен полностью значением справа, т.е. 0x00001000.

"|=" Используется что-бы затронуть (установить в 1 ) только нужные биты, а остальное оставить как есть. Как собственно и "^=" для их установки необходимых битов в 0.

Полагаю результат 0xFFFFFFFF был т.к. этот регистр был заполнен этим значением по-умолчанию или ранее. (Не разбирался взял ваше значение за основу)

Относительно адруинщиков или как там их. Да, практика визуально определять биты пришла оттуда, а может и ещё раньше от АTMEL-щиков. Отсюда и происходят строки кода типа.

RALINK_REG(RALINK_PIO_BASE+PIO_SET1) |= (1<< SOME_DATA_BIT);

Как показывает практика, в процессе конфигурации лучше стразу устанавливать весь регистр целиком RALINK_REG(RALINK_PIO_BASE+PIO_SET1) = 0x12345678; //0x12345678 необходимое значение

Это сокращает кол-во кода, но правда усложняет его восприятие (помогают комментарии ). Используется это тогда, когда память МК ограничена или её очень мало, например целых 8кб

). Используется это тогда, когда память МК ограничена или её очень мало, например целых 8кб  .

.

З.Ы. Расписал подробно с целью более-менее раскрыть вопрос. Цели задеть Вас не преследовал, думаю Вы всё это и так знаете.

Выражение a != b подразумевает a = a | b, т.е. побитовое ИЛИ над a и bЗнак "=", а не "|=".

В итоге, в коде от Linkit, получаем RALINK_REG(RALINK_PIO_BASE+PIO_SET1) = 0xFFFFFFFF;

Насколько мне известно побитовое ИЛИ устанавливает в 1 результат бита, где хотя-бы один из двух (а или b) имеет этот бит равным 1 ?

Далее, выражение ( 1<<12 ) подразумевает сдвиг 1 на 12 бит влево, т.е. все остальные биты это нули, результат-же такой 0x00001000 или в двоичном виде b 000 0000 0000 0000 0000 1000 0000 00000.

Побитовое ИЛИ для 0xFFFFFFFF | 0x00001000 = > 0xFFFFFFFF (что вполне естественно). Если поставить просто знак равенства, то регистр будет заполнен полностью значением справа, т.е. 0x00001000.

"|=" Используется что-бы затронуть (установить в 1 ) только нужные биты, а остальное оставить как есть. Как собственно и "^=" для их установки необходимых битов в 0.

Полагаю результат 0xFFFFFFFF был т.к. этот регистр был заполнен этим значением по-умолчанию или ранее. (Не разбирался взял ваше значение за основу)

Относительно адруинщиков или как там их. Да, практика визуально определять биты пришла оттуда, а может и ещё раньше от АTMEL-щиков. Отсюда и происходят строки кода типа.

RALINK_REG(RALINK_PIO_BASE+PIO_SET1) |= (1<< SOME_DATA_BIT);

Как показывает практика, в процессе конфигурации лучше стразу устанавливать весь регистр целиком RALINK_REG(RALINK_PIO_BASE+PIO_SET1) = 0x12345678; //0x12345678 необходимое значение

Это сокращает кол-во кода, но правда усложняет его восприятие (помогают комментарии

З.Ы. Расписал подробно с целью более-менее раскрыть вопрос. Цели задеть Вас не преследовал, думаю Вы всё это и так знаете.

Пару дней назад начал разбираться с омегой. Точнее так, омега валялась давно, даже развел и заказал платку под определенную задачу. За эти пару дней - спаял, запустил и написал немножко кода.Только омега немножко собрана как "Device Mode" и свитч там не задействован вовсе.

Пины, которые шарятся с лановскими портами задействованы на другие, цифровые функции.

Заняв только один лановский порт как цифровой, который шарится с SPIS, другие пытался настраивать как аналоговые AGPIO_CFG, но как в дашике сказано

(note: When any bit of bit[20:17] is set to 1, P1 ~ P4 will be swtiched to digital PADs together.)

0: Analog PAD

1: Digital PAD

Как только один настроил как цифровой, остальные отваливаются.

Но это не последний прикол от медиатека.

Настраиваю все линии SPIS как gpio output, начинаю дрыгать линией SPIS_MISO.

Вижу дрыгается не только SPIS_MISO, но и SPIS_MOSI.

Дрыгаю линией SPIS_MOSI, дрыгается только она, опять начинаю дрыгать линией SPIS_MISO и болезнь прошла, дрыгается только SPIS_MISO, а SPIS_MOSI уже не дрыгается как в первом случае.

Появилась задача - для реализации которой необходимо 2а езернета. Цитаруемые Вами строки в даташите нашёл, но ситуацию это не особо прояснило. Этому даташиту, по-наполнению до STM-овских очень далеко.

Первым был порыв конфигурировать регистры на прямую прям из линукса, на этом этапе написал (на golang) софтинку читающую данные из регистров и выводящую в удобном виде ( HEX Маленьких и Больших индейцев, а также бин и стринг), что-то расширенного devmem.

Писать в не пробовал, решил сначала ознакомиться с полной принципиальной схемой омеги и омеги+ (пока не нашел).

Я так понимаю. тот Ethernet, который выведен на омеге это WAN, а при активации любого из P1-P4 мы активируем SWITCH.

В общем, у меня несколько вопросов к Вам и другим участникам форума:

0. Где можно глянуть полную принципиальную схему по омеге ?

1. Как из Device Mode перевести в Switch/gateway Mode путём редактирования конфига(ов) в source (Я так понял Вы делали это именно так) ?

2. Если просто активировать switch mode изменением регистра не станет-ли плохо омеге/омеге+ учитывая текущую распаянную элементную базу?

Всем за ранее благодарен.

Алексей.

Active member

В открытом доступе не на омегу2 схем не встречал.0. Где можно глянуть полную принципиальную схему по омеге ?

Может я чего-то не разглядел в распиновке, только из 5-ти портов с чипа на улицу выведен (полностью) только один P0.Появилась задача - для реализации которой необходимо 2а езернета.

Код:

P1_TP SPIS_CS/GPIO#14/PWM_CH0 НЕ ВЫВЕДЕН!

P1_TN SPIS_CLK/GPIO#15/PWM_CH1

RP_P1 SPIS_MISO/GPIO#16/UART_TXD2

RN_P1 SPIS_MOSI/GPIO#17/UART_RXD2

TP_P2 UART_TXD2/GPIO#20/PWM_CH2/SD_D5 НЕ ВЫВЕДЕН!

TN_P2 UART_RXD2/GPIO#21/PWM_CH3/SD_D4 НЕ ВЫВЕДЕН!

RP_P2 PWM_CH0/GPIO#18/SD_D7

RN_P2 PWM_CH1/GPIO#19/SD_D6

TP_P2 SD_WP/GPIO#22 НЕ ВЫВЕДЕН!

TN_P3 SD_CD/GPIO#23 НЕ ВЫВЕДЕН!

RP_P3 SD_D1/GPIO#24 НЕ ВЫВЕДЕН!

RN_P3 SD_D0/GPIO#25 НЕ ВЫВЕДЕН!

RP_P4 SD_CLK/GPIO#26 НЕ ВЫВЕДЕН!

TN_P4 SD_D2/GPIO#27 НЕ ВЫВЕДЕН!

RN_P4 SD_CMD/GPIO#28 НЕ ВЫВЕДЕН!

TP_P4 SD_D3/GPIO#29 НЕ ВЫВЕДЕН!Там внутри, кроме чипа, стекляшки, флешки, рама и небольшой smd мелочевки, ничего нет, учитывать нечего.1. Как из Device Mode перевести в Switch/gateway Mode путём редактирования конфига(ов) в source (Я так понял Вы делали это именно так) ?

2. Если просто активировать switch mode изменением регистра не станет-ли плохо омеге/омеге+ учитывая текущую распаянную элементную базу?

В openwrt все уже отредактировано, выбираем подходящий профиль, собираем загружаем и настраиваем.

pvvx

Активный участник сообщества

А цель этого? Ранее указана явная ошибка и она в том, что производится чтение регистра и операция с этим значением, а при чтении данного регистра его значение всегда равно -1 и выставление нужных бит не происходит. Это вам не си и не методы, про что вы там калякаете, а аппаратная зависимость - данные регистры не предназначены для операции чтения.Прошу прощения, может это уже и "некро-ответ", но всё-же.

Выражение a != b подразумевает a = a | b, т.е. побитовое ИЛИ над a и b

Насколько мне известно побитовое ИЛИ устанавливает в 1 результат бита, где хотя-бы один из двух (а или b) имеет этот бит равным 1 ?

Далее, выражение ( 1<<12 ) подразумевает сдвиг 1 на 12 бит влево, т.е. все остальные биты это нули, результат-же такой 0x00001000 или в двоичном виде b 000 0000 0000 0000 0000 1000 0000 00000.

Побитовое ИЛИ для 0xFFFFFFFF | 0x00001000 = > 0xFFFFFFFF (что вполне естественно). Если поставить просто знак равенства, то регистр будет заполнен полностью значением справа, т.е. 0x00001000.

"|=" Используется что-бы затронуть (установить в 1 ) только нужные биты, а остальное оставить как есть. Как собственно и "^=" для их установки необходимых битов в 0.

Полагаю результат 0xFFFFFFFF был т.к. этот регистр был заполнен этим значением по-умолчанию или ранее. (Не разбирался взял ваше значение за основу)

Относительно адруинщиков или как там их. Да, практика визуально определять биты пришла оттуда, а может и ещё раньше от АTMEL-щиков. Отсюда и происходят строки кода типа.

RALINK_REG(RALINK_PIO_BASE+PIO_SET1) |= (1<< SOME_DATA_BIT);

Как показывает практика, в процессе конфигурации лучше стразу устанавливать весь регистр целиком RALINK_REG(RALINK_PIO_BASE+PIO_SET1) = 0x12345678; //0x12345678 необходимое значение

Это сокращает кол-во кода, но правда усложняет его восприятие (помогают комментарии). Используется это тогда, когда память МК ограничена или её очень мало, например целых 8кб

.

З.Ы. Расписал подробно с целью более-менее раскрыть вопрос. Цели задеть Вас не преследовал, думаю Вы всё это и так знаете.

pvvx

Активный участник сообщества

0. Где можно глянуть полную принципиальную схему по омеге ?

GitHub - OnionIoT/Onion-Hardware: Schematic of Onion Omega2 Docks and Expansions

Schematic of Onion Omega2 Docks and Expansions. Contribute to OnionIoT/Onion-Hardware development by creating an account on GitHub.