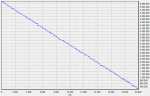

По нужде ещё раз глянул работу ADC в XT-ZB1 Devkit. Нужно было что-то дешевое и с более 14 бит ENOD для подключения INA199A1.

В принципе, используя железные китайские проводки и разъемы к XT-ZB1 Devkit - всё на соплях, но вроде влезает, если до 20 ksps в USB-CDC.

Варианты ADC sps в BL702 от CLK_DIV и AVERAGE:

// ADC_CLOCK_DIV_32, ADC_DATA_WIDTH_16B_WITH_256_AVERAGE = 3906.25 sps # 32000000/256/32 = 3906.25

// ADC_CLOCK_DIV_24, ADC_DATA_WIDTH_16B_WITH_256_AVERAGE = 5208.33 sps # 32000000/256/24 = 5208.33

// ADC_CLOCK_DIV_20, ADC_DATA_WIDTH_16B_WITH_256_AVERAGE = 6250 sps # 32000000/256/20 = 6250

// ADC_CLOCK_DIV_16, ADC_DATA_WIDTH_16B_WITH_256_AVERAGE = 7812.5 sps # 32000000/256/20 = 7812.5

// ADC_CLOCK_DIV_12, ADC_DATA_WIDTH_16B_WITH_256_AVERAGE = 10416.66 sps # 32000000/256/12 = 10416.66

// ADC_CLOCK_DIV_32, ADC_DATA_WIDTH_16B_WITH_128_AVERAGE = 7812.5 sps # 32000000/128/32 = 7812.5

// ADC_CLOCK_DIV_24, ADC_DATA_WIDTH_16B_WITH_128_AVERAGE = 10416.66 sps # 32000000/128/24 = 10416.66

// ADC_CLOCK_DIV_20, ADC_DATA_WIDTH_16B_WITH_128_AVERAGE = 12500 sps # 32000000/128/20 = 12500

// ADC_CLOCK_DIV_16, ADC_DATA_WIDTH_16B_WITH_128_AVERAGE = 15625 sps # 32000000/128/16 = 15625

// ADC_CLOCK_DIV_12, ADC_DATA_WIDTH_16B_WITH_128_AVERAGE = 20833.33 sps # 32000000/128/12 = 20833.33

// ADC_CLOCK_DIV_32, ADC_DATA_WIDTH_14B_WITH_64_AVERAGE = 15625 sps # 32000000/64/32 = 15625

// ADC_CLOCK_DIV_24, ADC_DATA_WIDTH_14B_WITH_64_AVERAGE = 20833.33 sps # 32000000/64/24 = 20833.33

// ADC_CLOCK_DIV_20, ADC_DATA_WIDTH_14B_WITH_64_AVERAGE = 25000 sps # 32000000/64/20 = 25000

// ADC_CLOCK_DIV_16, ADC_DATA_WIDTH_14B_WITH_64_AVERAGE = 31250 sps # 32000000/64/16 = 31250

// ADC_CLOCK_DIV_12, ADC_DATA_WIDTH_14B_WITH_64_AVERAGE = 41666.66 sps # 32000000/64/12 = 41666.66

// ADC_CLOCK_DIV_32, ADC_DATA_WIDTH_14B_WITH_16_AVERAGE = 62500 sps # 32000000/16/32 = 62500

// ADC_CLOCK_DIV_24, ADC_DATA_WIDTH_14B_WITH_16_AVERAGE = 83333.33 sps # 32000000/16/24 = 83333.33

// ADC_CLOCK_DIV_20, ADC_DATA_WIDTH_14B_WITH_16_AVERAGE = 100000 sps # 32000000/16/20 = 100000

// ADC_CLOCK_DIV_16, ADC_DATA_WIDTH_14B_WITH_16_AVERAGE = 125000 sps # 32000000/16/16 = 125000

// ADC_CLOCK_DIV_12, ADC_DATA_WIDTH_14B_WITH_16_AVERAGE = 166666.66 sps # 32000000/16/12 = 166666.66

// ADC_CLOCK_DIV_32, ADC_DATA_WIDTH_12B = 100000 sps # 32000000/32 = 1000000

// ADC_CLOCK_DIV_24, ADC_DATA_WIDTH_12B = 1333333.33 sps # 32000000/24 = 1333333.33

// ADC_CLOCK_DIV_20, ADC_DATA_WIDTH_12B = 1600000 sps # 32000000/20 = 1600000

// ADC_CLOCK_DIV_16, ADC_DATA_WIDTH_12B = 2000000 sps # 32000000/16 = 2000000

// ADC_CLOCK_DIV_12, ADC_DATA_WIDTH_12B = 2666666.66 sps # 32000000/12 = 2666666.66

Использовал ADC_CLOCK_DIV_12, ADC_DATA_WIDTH_16B_WITH_128_AVERAGE = 20833.33 sps (более уверенно не лезет в USB без оптимизации исходников SDK)