От вас нужны PR в upstream. Иначе это труд в помойку.

Он не нужен, т.к. у MT7688A баг.

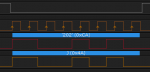

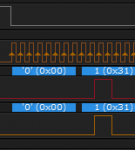

Она сжирает первый бит блока данных буфера на передачу. Хотите передать 0x80 - передаст 0x00 (на осциллограмме вообще не будет даже импульсa).

И если выставляется первый бит передачи из блока данных буфера (например передаем 0xFF) то это происходит одновременно с активным стробом фронта CLK.

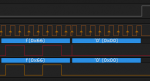

И это не полное описание бага - там первый бит пересекается со вторым. И пофигу какие установки от старшего к младшему или наоборот, режимы 0..3, имеющиеся задержки....

На самой низкой скорости:

root@OpenWrt:/# spidev_test -D /dev/spidev0.1 -s 50000 -p "\xCA" -v

spi mode: 0x0

bits per word: 8

max speed: 50000 Hz (50 KHz)

TX | CA __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ | К

RX | 4A __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ | J

root@OpenWrt:/# spidev_test -D /dev/spidev0.1 -s 50000 -p "\xFF" -v

spi mode: 0x0

bits per word: 8

max speed: 50000 Hz (50 KHz)

TX | FF __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ | .

RX | 7F __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ |

root@OpenWrt:/# spidev_test -D /dev/spidev0.1 -s 50000 -p "\x80123456789abcdef\x80" -v

spi mode: 0x0

bits per word: 8

max speed: 50000 Hz (50 KHz)

TX | 80 31 32 33 34 35 36 37 38 39 61 62 63 64 65 66 80 __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ | Ђ123456789abcdefЂ

RX | 00 31 32 33 34 35 36 37 38 39 61 62 63 64 65 66 00 __ __ __ __ __ __ __ __ __ __ __ __ __ __ __ | .123456789abcdef.

Но чтение работает.

Т.е. если в дровах выбираем длину передающего буфера в 16 байт, то каждый 16-й не должен иметь активный старший бит... Так жить можно.

Закрытая - нарушение GPL!

Ни в коем разе. Если кто получит устройство и по его особой просьбе будут выданы исходники - сразу все, кучей в Гега-Террабайты, без разбору и уточнений - пусть всю жизнь ищет зависимости и прочее

не ждет полного завершения передачи.

не ждет полного завершения передачи.